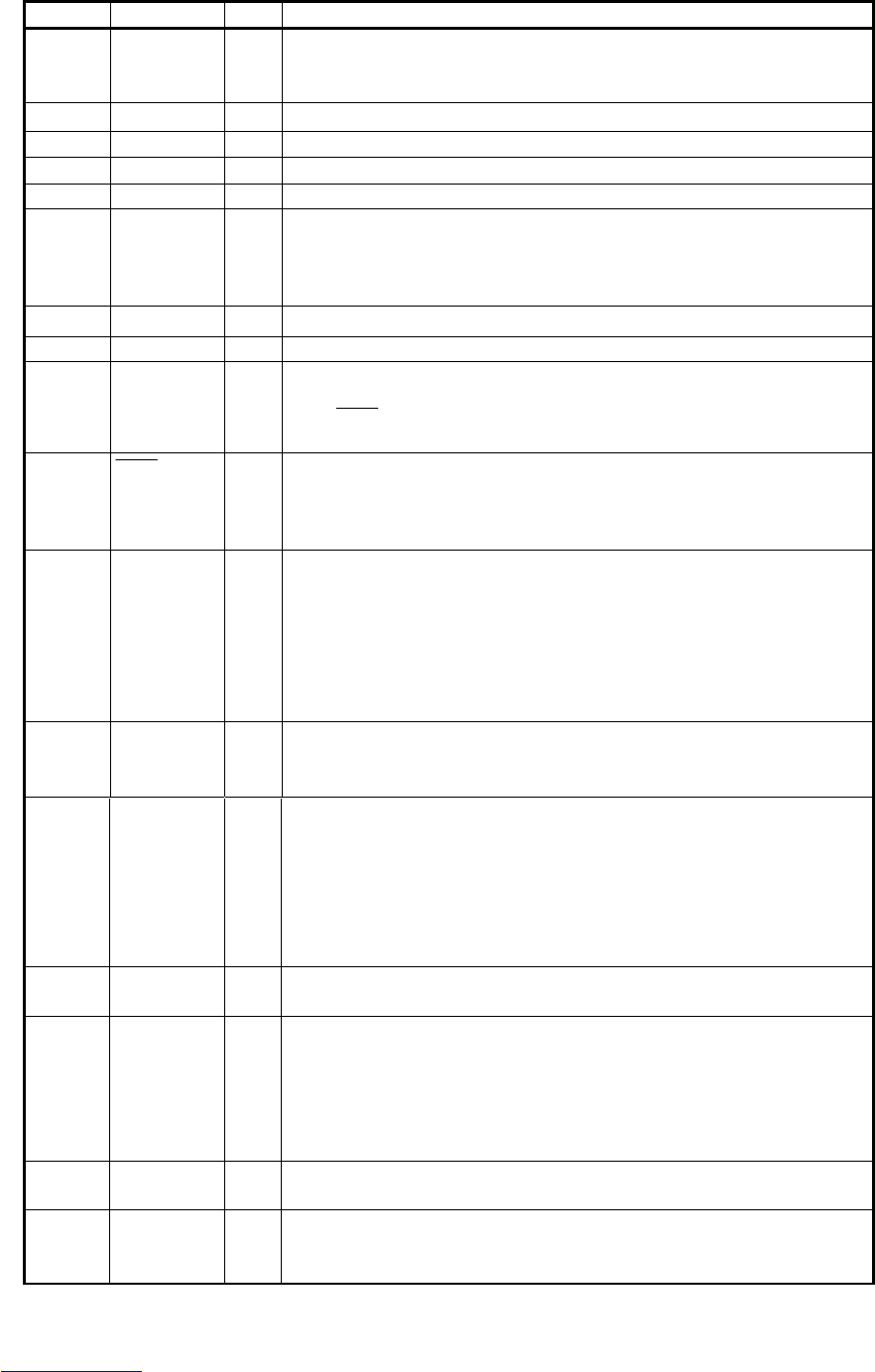

56

No. Pin Name I/O Function

1 VREFL O Lch Reference Voltage Pin, 3.75V

Normally connected to GNDL with a 10µ

F electrolytic capacitor and

a 0.1µF ceramic capacitor.

2 GNDL - Lch Reference Ground Pin, 0V

3 VCOML O Lch Common Voltage Pin, 2.75V

4 AINL+ I Lch Analog positive input Pin

5 AINL- I Lch Analog negative input Pin

6 ZCAL I Zero Calibration Control Pin

This pin controls the calibration reference signal.

"L": VCOML and VCOMR

"H": Analog Input Pins ( AINL ±, AINR±)

7VD -Digital Power Supply Pin, 3.3V

8 DGND - Digital Ground Pin, 0V

9CAL OCalibration Active Signal Pin

"H" means the offset calibration cycle is in progress. Offset calibration starts

when RST

goes "H". CAL goes "L" after 8704 LRCK cycles for DFS="L",

17408 LRCK cycles for DFS =

"H".

10

RST

I Reset Pin

When "L", Digital section is powered-down. Upon returning "H", an

offset calibration cycle is started. An offset calibration cycle should always

be initiated after power-up.

11

12

SMODE2

SMODE1

I

I

Serial Interface Mode Select Pin

MSB first, 2's compliment.

SMODE2 SMODE1 MODE LRCK

L

L Slave mode : MSB justified : H/L

L H Master mode : Similar to I

2

S : H/L

H L Slave mode : I

2

S

:

L/H

H H Master mode

: I

2

S : L/H

13 LRCK I/O Left/Right Channel Select Clock Pin

LRCK goes "H" at SMODE2="L" and "L" at SMODE2="H" during reset

when SMODE1 "H".

14 SCLK I/O Serial Data Clock Pin

Data is clocked out on the falling edge of SCLK.

Slave mode:

SCLK requires more than 48fs clock.

Master mode:

SCLK outputs a 128fs(DFS="L") or 64fs(DFS="H") clock.

SCLK stays "L" during reset.

15 SDATA O Serial Data Output Pin

MSB first, 2's complement. SDATA stays "L" during reset.

16 FSYNC I/O Frame Synchronization Signal Pin

Slave mode:

When "H", the data bits are clocked out on SDATA. In I

2

S mode, FSYNC is

Don’t care.

Master mode:

FSYNC outputs 2fs clock. FSYNC stays "L" during reset.

17 MCLK I Master Clock Input Pin

256fs at DFS="L", 128fs at DFS="H".

18 DFS I Double Speed Sampling Mode Pin

"L": Normal Speed

"H": Double Speed

Pin Description

QK51 : AK5383